Síntesis de Sistemas Digitales: VHDL, componentes virtuales, dispositivos programables

|

Síntesis de Sistemas Digitales: VHDL, componentes virtuales, dispositivos programables |

|

|

|

|

|

Detalles del Curso

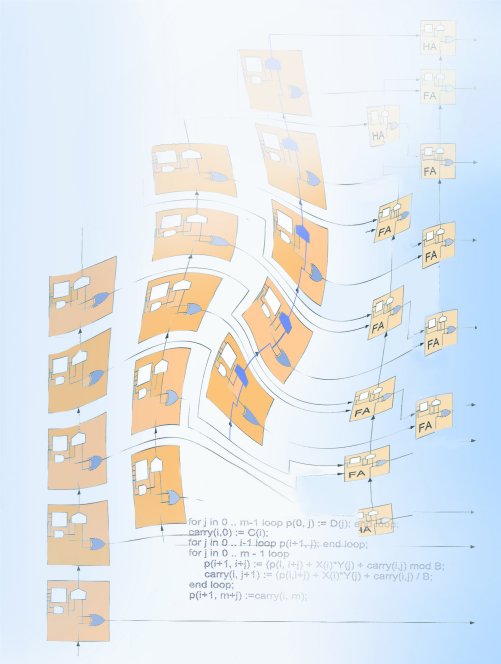

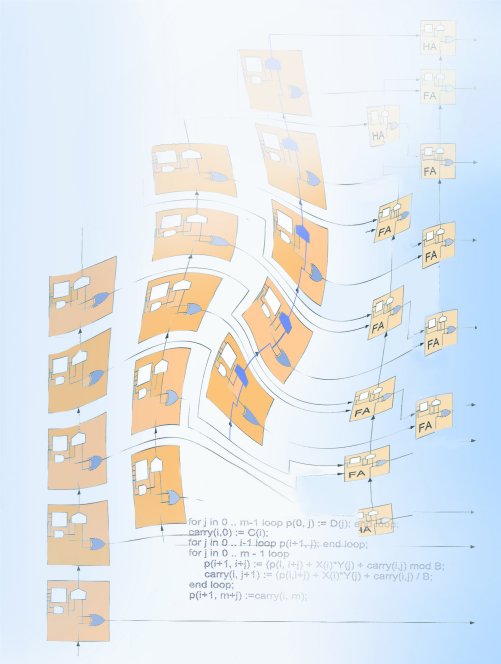

Programa:I Introduction to embedded systems: 1 Characteristics 2 Generic architecture 3 Main development steps 4 Implementation technologies 5 Development tools II VHDL 1 Logic signal model 2 Main predefined operations 3 Model types 4 Gate network models 5 Multiplexer models 6 Inferred latches 7 Combinational circuits defined by a table 8 Iterative circuits 9 User defined package 10 Arithmetic circuits 11 Tri-state buffers 12 Flip-flops and registers 13 Counters 14 Finite State Machine 15 Memories 16 Hierarchy 17 Using variables 18 Important concepts III Programmable devices 1 PLD – Programmable Logic Devices 2 CPLD - Complex Programmable Logic Device 3 FPGA - Field Programmable Gate Array 4 Programming technologies 5 LUT – Look-up tables 6 FPGA cell 7 Examples of FPGAs IV Virtual processors 1 Example of virtual processor: PicoBlaze 2 Spartan II implementation 3 Architecture 4 Component declaration 5 Instruction set 6 Input – Output operations 7 Assembling a program V An example 1 Specification 2 Hardware platform 3 Hardware – software partitioning 4 Program generation (software) 5 Program memory model 6 Circuit generation (hardware) Trabajos prácticos (generación de modelos VHDL, simulación, síntesis):

Pre-requisitos:conocimientos de circuitos digitales, arquitectura y aritmética de computadoras, programación. Calendario (5 días, 6 horas por día):día 1: Introduction, VHDL: 1 a 8 / tutorial: simulador (ModelSim) día 2: VHDL: 9 y 10, ejemplos de circuitos combinacionales / trabajo práctico 1 día 3: VHDL:11 a 13, ejemplos de circuitos secuenciales, VHDL: 14 a 18 / trabajo práctico 2 día 4: ejemplos de máquinas algorítmicas (data path + control unit), Programmable devices / trabajo práctico 3, tutorial: herramienta de síntesis (ISE) día 5: Virtual processors, An example / trabajo práctico 4, presentación del proyecto final Evaluación final:después de finalizar el curso, cada estudiante dispondrá de dos meses para la realización de un proyecto final que será enviado a los profesores por correo

|

This site was last updated 06/26/07